Fritzchens Fritz 氏により、RDNA 2 アーキテクチャ を採用する Navy Flounder/Navi22 のダイショットが公開された。

Intel は最近 CPU のダイショットを積極的に公開しているようには感じるが、研究発表の場以外では大体の場合において、内部構造を模した CG か一部を置き換えた、あるいはぼかしたものがダイショットの代わりに使われることが多い。そのため、スキルある人が得たデータを広くに公開してくれることはは貴重である。

氏の測定によれば、Navy Flounder/Navi22 のダイサイズは 334.980mm2、そう変わらないが RX 6700 XT 発表時に AMD が公表したダイサイズは 336mm2 だった。1

Index

Infinity Cache/MALL/L3キャッシュ

RDNA 2 dGPU から導入された、マーケティング的には Infinity Cache 、オープンソース・ドライバー中では MALL (Memory Access at Last Level) 、キャッシュ階層で言えば L3キャッシュに当たるそれは、Navy Flounder/Navi22 には 96MiB 搭載されている。

ダイショットにおいて L3キャッシュブロックはかなり目立ち、上下部に敷き詰めるようにして配置されている。

Navy Flounder/Navi22 のメモリインターフェイスは GDDR6 192-bit (16-bit x12ch)、メモリチャネルあたりの L3キャッシュサイズは 8MiB となるが、ダイショットでは 16ブロック確認でき、ブロックあたり 4MiB の実装となっている。

Navy Flounder/Navi22 より小規模な構成を採る RDNA 2 dGPU、Dimgrey Cavefish/Navi23、Beige Goby/Navi24 は、メモリチャネルあたりの L3キャッシュが 4MiB となっており、ブロックあたりのサイズと一致する。

それらにおいては、おそらくブロック (4MiB) の設計は基本そのままに、メモリチャネルあたり 1ブロックとなるような実装になっているのではないかと思われる。

Dimgrey Cavefish/Navi23 の Infinity Cache はメモリチャネルあたり 4MiB | Coelacanth’s Dream

新たな RDNA 2 GPU、「Beige Goby」 をサポートするパッチが投稿される | Coelacanth’s Dream

また GPU L3キャッシュは、VanGogh、Yellow Carp/Rembrandt といった RDNA 2 アーキテクチャ を採用する APU では搭載されていないことが明らかにされている。

AMD GPU のキャッシュ構成情報 ―― Dimgrey Cavefish / Aldebaran / VanGogh | Coelacanth’s Dream

| RDNA 2 | Sienna Cichlid/Navi21 | Navy Flounder/Navi22 | Dimgrey Cavefish/Navi23 |

|---|---|---|---|

| WGP (CU) | 40 (80) | 20 (40) | 16 (32) |

| Memory bus width | 256-bit | 192-bit | 128-bit |

| L3 cache | 128MiB | 96MiB | 32MiB |

| Transistor count | 26.8M | 17.2B | 11.1B |

| Die size | 519mm2 | 336mm2 | 223mm22 |

WGP 20基 (CU 40基) というくくりでは、Navi10 と同じ。

Navy Flounder/Navi22 は Navi10 から、RB+ の有効化を前提としたことにより RB+ の実装面積を削減 (16基 -> 8基)、メモリバス幅の削減 (256-bit -> 128-bit) といったダイサイズを節約できる要素があるが、

一部の AMD GPU で実装、有効化されている RB+ とは何か | Coelacanth’s Dream

L3キャッシュ追加の影響が大きく、結果としてダイサイズは約 1.34倍となっている。(Navi10: 251mm2)

L3キャッシュ 比較

RDNA 2 L3キャッシュは Zen アーキテクチャ のデザインをベースにしていることが AMD より語られており、それによって高密度、高クロック動作を可能にしているとする。

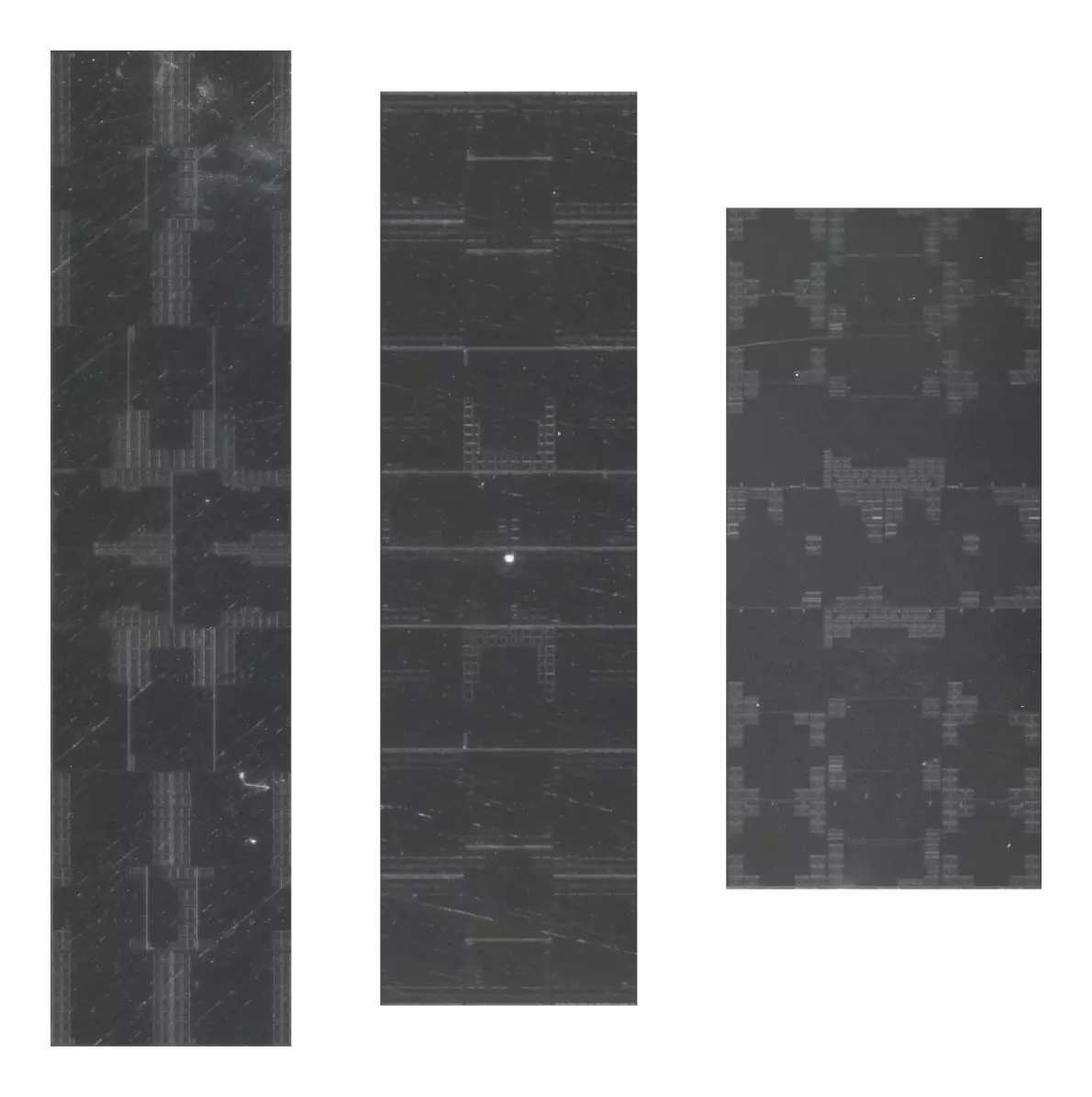

以下は Navy Flounder/Navi22 の L3キャッシュブロック (4MiB) と、Zen 3 アーキテクチャ の L3キャッシュスライス (4MiB) を並べた画像。

Zen 3 のダイショットも Fritzchens Fritz 氏が撮影したものを用いている。

4MB Cache: Navy Flounder/Navi22・Zen 3

画像出典:

AMD@7nm@RDNA_2nd_gen@Navi22@Radeon_RX_6700_XT@215-0932396@… | Flickr,

AMD@7nm(12nmIOD)@Zen3@Vermeer@Ryzen_5_5600X@100-000000064_… | Flickr

Zen 3 L3キャッシュには LDO (Low-Dropout regulator) と V-Cache のための TSV部が含まれている。

そうした点もあるが、Navy Flounder/Navi22 ではタグが Zen 3 よりも少ない構成となっている。タグは Navy Flounder/Navi22 では下部、Zen 3 L3キャッシュでは中央左右に配置されている。

RDNA系アーキテクチャではキャッシュラインサイズが 128Byte であること、RDNA L3キャッシュは各メモリチャネルに対応したメモリサイドキャッシュだと考えられ、キャッシュコヒーレンシを維持する機構を必要としないことがより高密度な実装に繋がっているのではないかと思われる。

| L3 4MiB | RDNA 2 | Zen 3 |

|---|---|---|

| Area | ~2.474mm2 | ~4.242mm2 |

WGP 比較

2 WGP: Navy Flounder/Navi22 ・ Navi14 ・ PS5

画像出典:

AMD@7nm@RDNA_2nd_gen@Navi22@Radeon_RX_6700_XT@215-0932396@… | Flickr,

AMD@7nm@RDNA_1th_gen@Navi14@Radeon_RX_5500_XT@215-0932396@… | Flickr,

AMD@7nm@Zen2_RDNA_APU@Oberon@PlayStation5@100-000000189_9J… | Flickr

向かい合うように配置された WGP 2基を、Navy Flounder/Navi22・Navi14・PS5 から切り出し、並べたのが上の画像。

サイズは実サイズに合わせたが、大体であり、あまり自信はない。

Navi14・PS5・Xbox Series X で比較したとき、PS5・XSX は同様の WGP レイアウトであることが見て取れたが、今回はそれぞれで部分的に異なっている。

PS5 のダイ観察 | Coelacanth’s Dream

また Navy Flounder/Navi22 と Navi14 の比較において、WGP のエリアサイズはそれほど変わっていないように思う。

WGPレベルでの RDNA から RDNA 2 の変更点には、レイトレーシング対応と、SIMDユニットあたりの Waveバッファを 20エントリから 16エントリに減らしたことが挙げられる。(ドット積命令に関しては Navi14 との比較では変わらない)

逆に、製造プロセスが変わらないからこそ WGPレベルでは大きな変更を取り入れなかったのかもしれない。

また、実サイズに即している自信がない理由でもあるのだが、PS5 の WGP は他 2つと比べて明らかに小さい。

WGP 2基を並べた中心に位置する、TMU (Texture Mapping Unit) + RA (Ray Accelerator) 4基のレイアウトは、PS5・XSX では L字ブロックを組み合わせたような配置になっている。

それ以外の部分、SIMD32ユニット 4基や LDS などのメモリもロジック部が小さくなっているように見える。

| WGP 2-units | compare with Navi14 |

|---|---|

| Navy Flounder | x1.02 |

| Navi14 | x1.00 |

| PS5 | x0.92 |