Fritzchens Fritz 氏により、PS5 SoC のダイショットが公開された。

Xbox Series X SoC は HotChips 32 にて既に公開されており、そのため今まで隠されていた PS5 SoC の構造には注目が集まっていた。

Index

FPU の規模を小さくした PS5 CPU

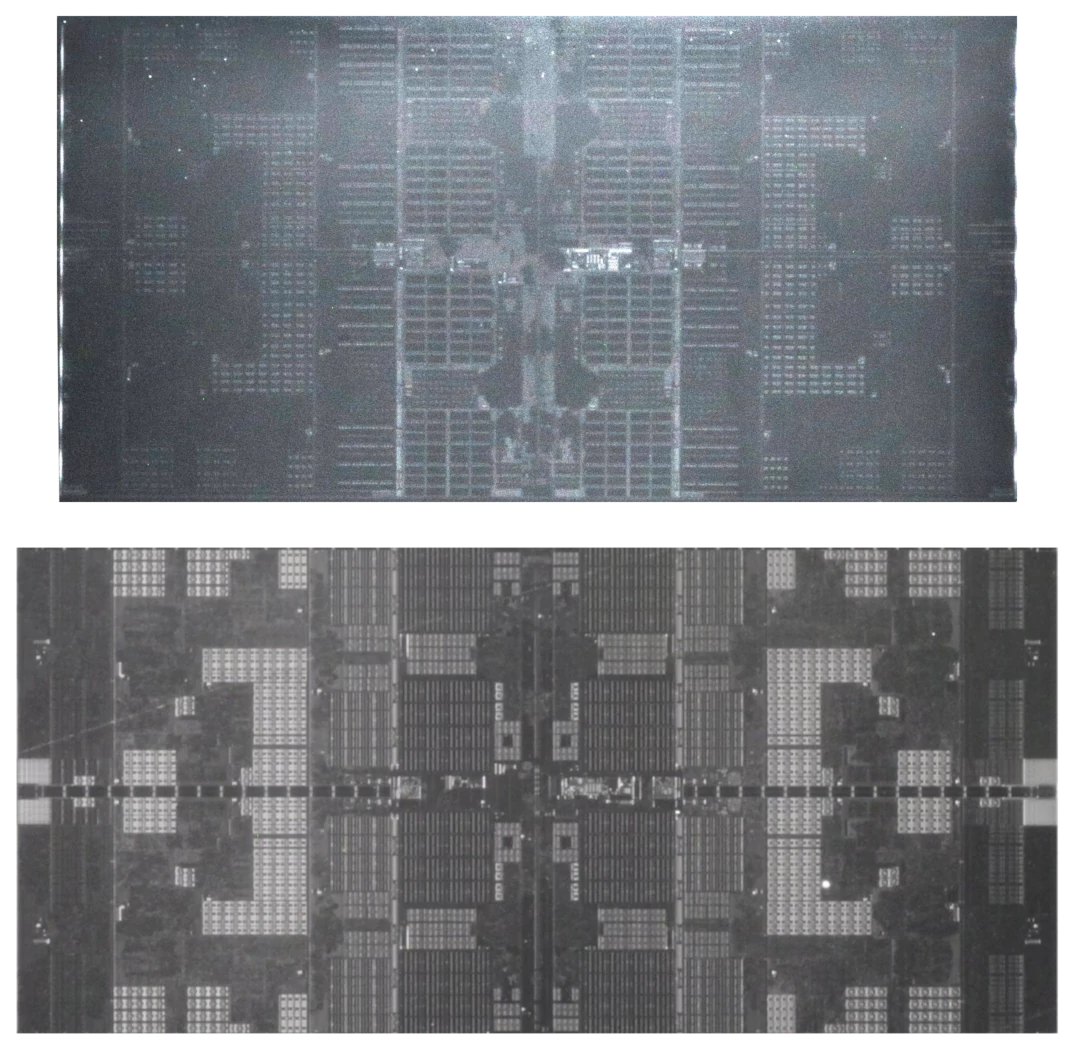

↑ PS5 4-Core CCX / ↓ Renoir 4-Core CCX

画像元:

↑ DSC02283# | quick and dirty test shot | Fritzchens Fritz | Flickr

↓ AMD@7nm@Zen2@Renoir@Ryzen_3_4300U@100-000000085_9JB4977P00… | Flickr

PS5 CPU の 4-Core CCX と Renoir APU の Zen2 4-Core CCX をとりあえず縦幅を合わせ、並べた画像が上。実際の面積等は考慮していない。

コアの外側端、Renoir と比較して PS5 CPU の面積が少なくなっている部分は、AMD が ISSCC 2020 にて発表した Zen 2 コアの概要によると、FPU (Floating Point Unit) にあたり、1

撮影を行った Fritzchens Fritz 氏が言及したように、PS5 では FPU の規模を小さくした設計となっている。

恐らくは FPU のデータ幅を Zen 2 の 256-bit から 128-bit にしたものと考えられる。FPU の演算パイプ数を減らすと各 FPU の構成やスケージューラーを変える必要が出てしまうし、コンパイラ側の最適化等も変えなければならない。

Zen 2 アーキテクチャ では、FPU に演算パイプを 4本持ち、MUL 2本、ADD 2本と一見対称になっているが、「Software Optimization Guide for AMD Family 17h Models 30h and Greater Processors (Page36)」 を見るに実際は完全に対称ではなく、ある処理を行えるのが 1本だけということがある。

これを変えて再構成するのは手間だろう。

FPU を減らしたこと自体については、FP性能が必要であれば GPU で処理すればよく、CPU側の FP性能はあまり必要無いと考えたのかもしれない。前世代の PS4/Pro は CU、演算ユニットの規模に対し、フロントエンドの ACE (Asynchronous Compute Engine) を多く搭載し、GPU をより汎用的に使いやすくした設計だった。

PS4/Pro で採用された Jaguar コアもまた FPU のデータ幅は 128-bit であるため、互換性を取る上で Zen 2 コアの FPU は無駄があると考えた可能性もある。

Zen 2 コアそのままではなく、面積を減らし、製造コストをより小さくしようとした工夫は、汎用機ではないゲーム機用の SoC として印象的な変更である。

同様に Zen 2 コアを採用している Xbox Series X は 256-bit幅であり、そのままの構成を採っている。

Navi14/PS5/XSX WGP比較

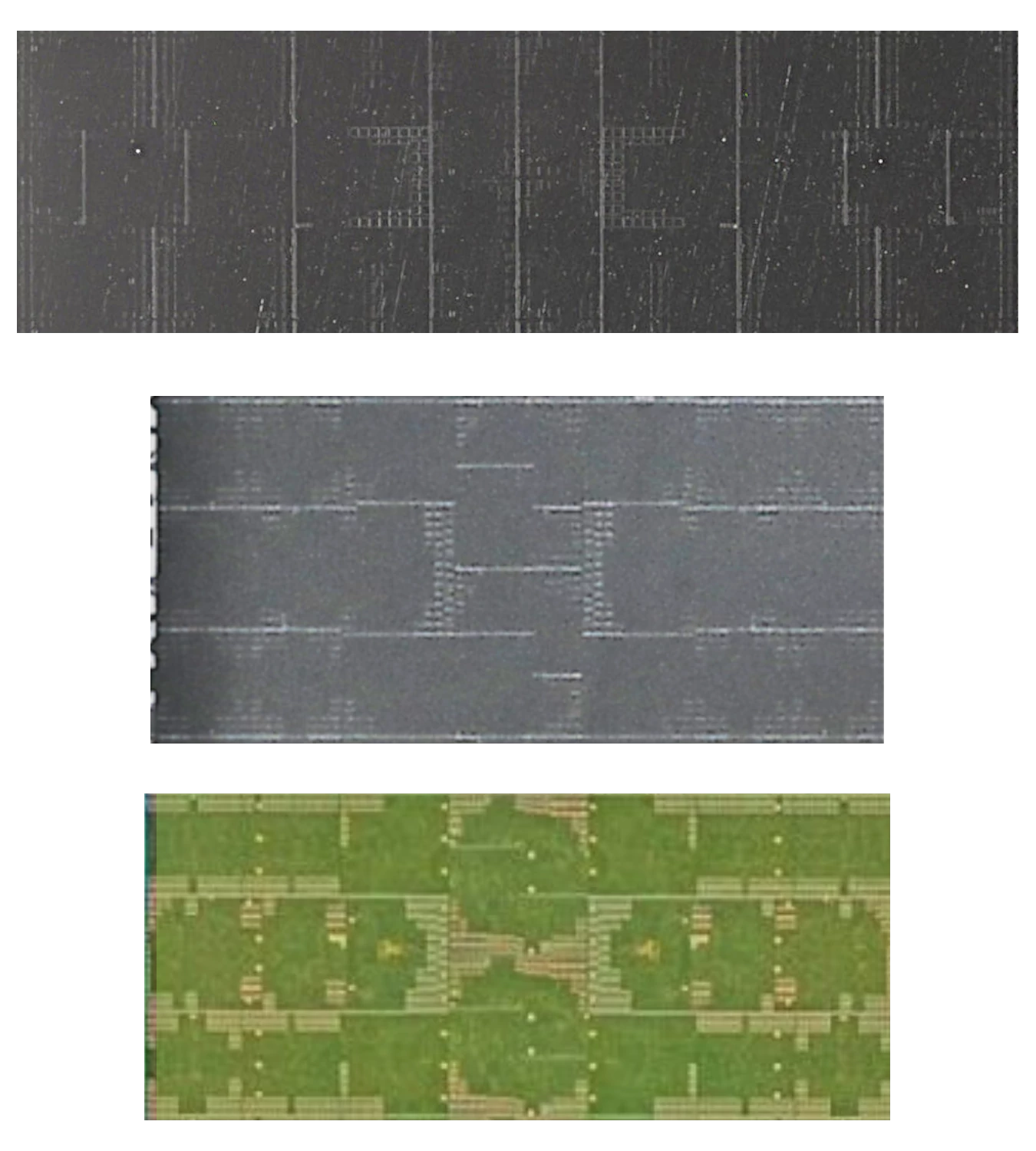

T: Navi14 (RDNA) 2-WGP / M: PS5 2-WGP / D: XSX 2-WGP

画像出典:

T: AMD@7nm@RDNA_1th_gen@Navi14@Radeon_RX_5500_XT@215-0932396@… | Flickr

M: DSC02280 | quick and dirty test shot | Fritzchens Fritz | Flickr

D: HotChips2020_GPU_Microsoft_Jeff_Andrews_v2.pdf

Navi14 (RDNA) 、PS5 、XSX の対称的に配置された 2基の WGP を並べた画像が上。

こちらは、3つともメモリに GDDR6 を採用しており、そして WGP の近くにプロセスの微細化の影響を受けにくい GDDR6 PHY (物理層) があったため、それを基準にサイズを合わせている。

WGP 2基で比較したのは、配置によっては一部ユニットの構造や専有面積が変わることがあり、その差を減らすため。

Navi21 (RDNA 2) の詳細なダイショットは無いため、あくまでも Navi14 (RDNA) と RDNA 2 ベースとの比較となる。

まず言えるのは、PS5 2-WGP と XSX 2-WGP の面積は近く、Navi14 2-WGP の約8割となっていることだ。

PS5 と XSX の WGP は Navi14 のそれより若干縦に大きくなっているが、全体的にコンパクトに収められている。

製造プロセスについては、Navi14 は TSMC 7nm だが、PS5 は 7nm、そして XSX は 7nm Enhanced という言葉を用いており、曖昧な所があるが、PS5 と XSX は Navi14 の TSMC 7nm より進んだ 7nmプロセスで製造されているとも見られる。物理設計の最適化による功績である可能性もあるが。

面積だけでなく、中央部、TMU (Texture Mapping Unit) + RA (Ray Accelerator) 4基の構造も近いものとなっており、画像を拡大すると分かりやすい。これが Navi21 (RDNA 2) と同様かが一層気になる所だ。

ただ、やはり同時期に同じ開発企業と協力して設計する以上、似通うものなのだろう。

| 2-WGP | Pixels | vs Navi14 2-WGP |

|---|---|---|

| Navi14 | 514170px (W: 1305, H: 394) |

x1.00 |

| PS5 | 433068px (W: 956, H: 453) |

x0.84 |

| XSX | 414072px (W: 972, H: 426) |

x0.80 |

PS5 はダイに WGP 20基を搭載しているが、2基を歩留まり向上のため冗長ユニットとし、WGP 18基の製品仕様を満たしている。これは XSX でも同じで、WGP 28基中 2基を冗長ユニットとしている。

参考リンク

- PlayStation 5 Launches This November At $399 For PS5 Digital Edition, And $499 For PS5 With Ultra HD Blu-ray Disc Drive | Sony Corporation of America

- Xbox Series X

- 西川善司の3DGE:PS5のスペック予想はいくつ当たったか? CPUとGPUは予想どおりだが,最も意外なのはPrimitive Shaderの採用

- HC31_1.1_AMD_ZEN2.pdf

- HotChips2020_GPU_Microsoft_Jeff_Andrews_v2.pdf