次いで、Polaris10、Polaris11のユニット推測も、毎度お馴染みFritzchens Fritz | Flickr氏によるダイショットを元に行なった。

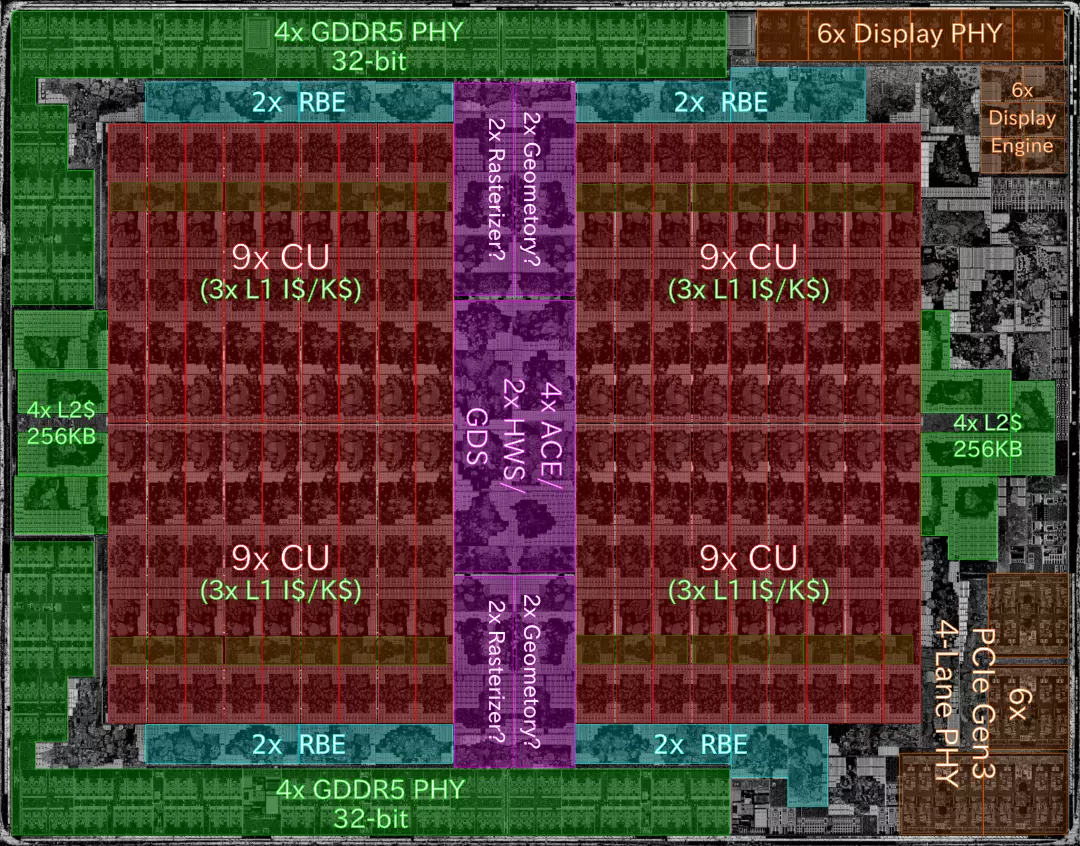

Polaris10

Polaris10 推測

ダイサイズ: 243.78mm2

画像出典:AMD@14nm@GCN\_4th\_gen@Polaris\_10@Radeon\_RX\_470@1622\_M60J5.0… | Flickr

ようやく自分なりの色分けとかやり方がわかってきた気がする。

それはともかく、GPUOpen-Drivers/pal: Platform Abstraction Libraryからの情報では1、

- 4-ShaderEngine

- ShaderEngineあたりのRBE(RenderBackend)数は4基

- 〃 のCU(ComputeUnit)数は9基

- TCC(L2cache)ブロック数は8基(ブロックあたり256KB、計2MB)

RadeonFeatureからの情報では、

- Display Controller数は6基

となっている。L1 I$(32KB)/K$(16KB)は3CUで共有する構成となっていた。

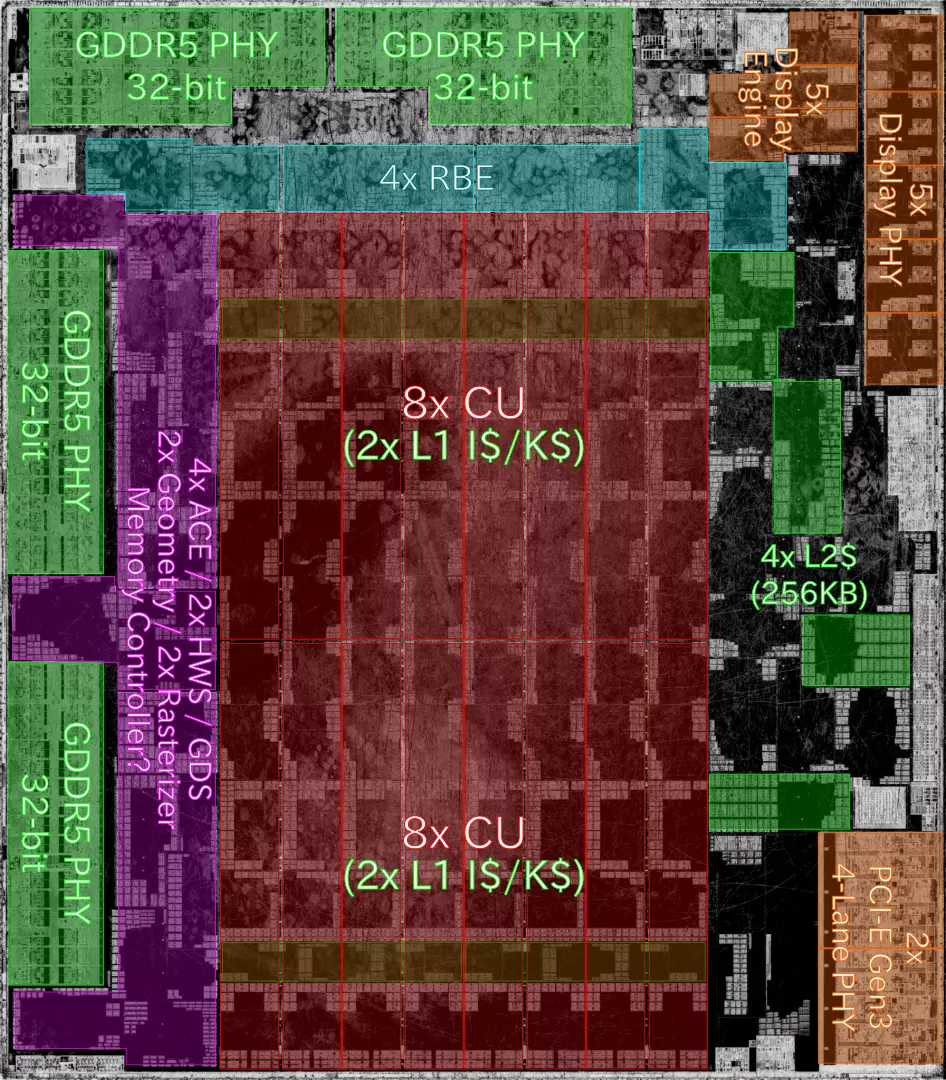

Polaris11

Polaris11 推測

ダイサイズ: 129.40mm2

画像出典:AMD@14nm@GCN\_4th\_gen@Polaris\_11@Radeon\_RX\_460@1628\_NAA2Y.1… | Flickr

129.40mm2と小型なダイだけあって、内部はより入り組んだ印象を受けた。

GPUOpen-Drivers/pal: Platform Abstraction Libraryからの情報では2、

- 2-ShaderEngine

- ShaderEngineあたりのRBE(RenderBackend)数は2基

- 〃 のCU(ComputeUnit)数は8基

- TCC(L2cache)ブロック数は4基(ブロックあたり256KB、計1MB)

RadeonFeatureからの情報では、

- Display Controller数は5基

となっている。L1 I$(32KB)/K$(16KB)は4CUで共有する構成となっていた。

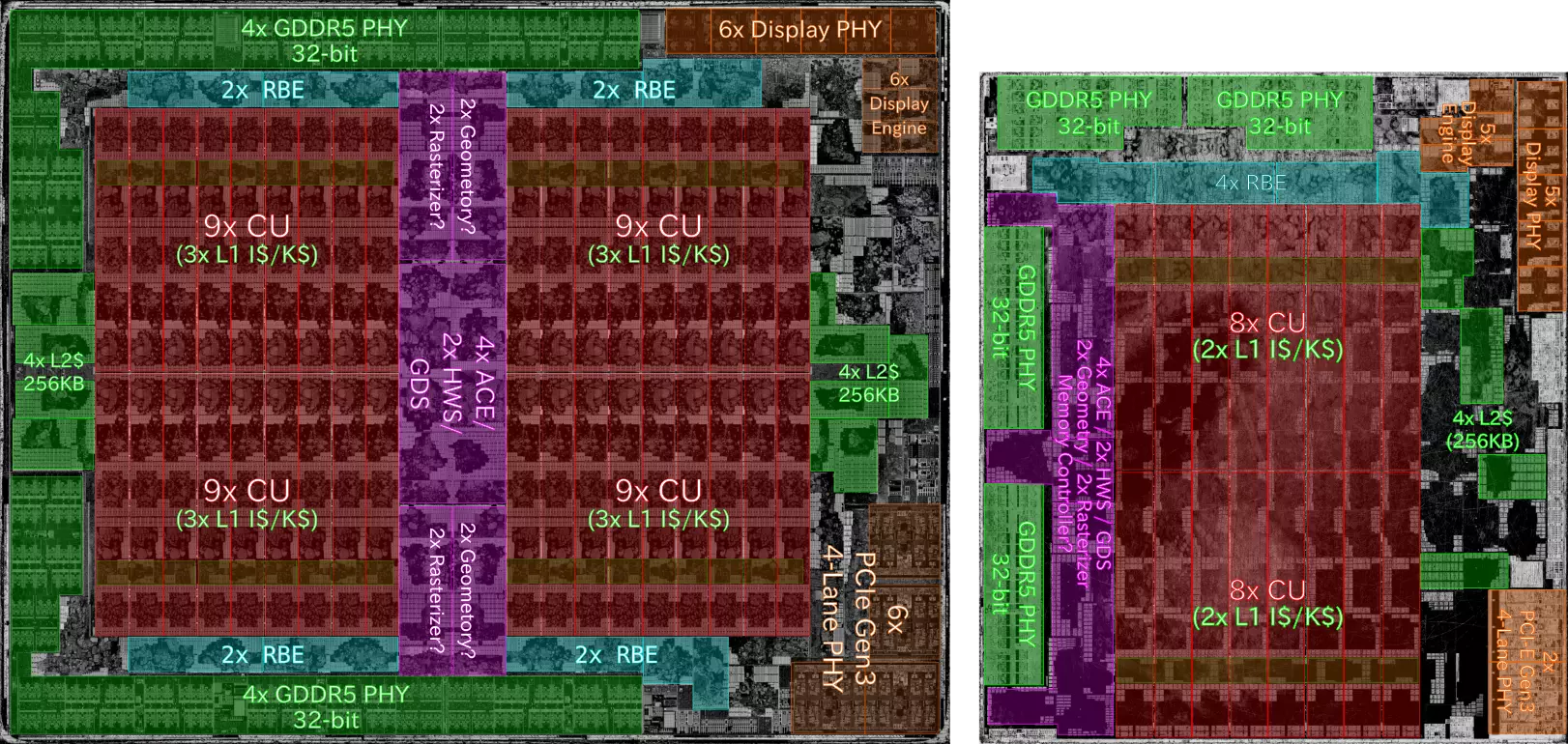

Polaris10とPolaris11の比較

L : Polaris10 / R : Polaris11

Process: GF 14nm / GF 14nm

DieSize: 243.78mm2 / 129.40mm2

画像出典:AMD@14nm@GCN\_4th\_gen@Polaris\_10@Radeon\_RX\_470@1622\_M60J5.0… | Flickr

AMD@14nm@GCN\_4th\_gen@Polaris\_11@Radeon\_RX\_460@1628\_NAA2Y.1… | Flickr

同プロセスで製造されているのだから、当然各ユニットのサイズもほぼ変わらず。

特筆することと言えば、L1 I$/K$を共有するCU数が Polaris10: 3基、Polaris11: 4基と違うことから、微妙に配置を変えていたことだろうか。高さは変わっておらず、内部だけの変更で対応していた。

ただそれは、3CU分に詰め込められるものを4CU分に引き伸ばしているとも取れ、そういった点でもGCNアーキテクチャには無駄があったと言える。

RDNAアーキテクチャでは、共有する数が2CU(1WGP)と固定された。これにより設計をわずかでも弄る手間が減ったのではないかと思う。

Polaris11とI/OやL2$の規模は変わらないが、CU数を減らし、ダイサイズも小さくなっているPolaris12も比較してみたかったが今回は無理だった。

どのように配置を工夫したのかはとても興味深いが……