以前、Raja Koduri氏によってパッケージとチップ外観が公開された Intel Ponte Vecchio GPU だが、今回 47個のタイルで構成されることが新たに明かされた。

Raja Koduri氏が Xe-HPC のチップ構成とパッケージを公開 | Coelacanth’s Dream

Raja Koduri氏は 47個のタイルの内訳について、以下のように説明している。

以前は 41個のタイルとしていたらしいが、これは HBM2eメモリを個々のタイルとして計上していなかったとのこと。Ponte Vecchio は 2つの Base Tile を搭載し、そこに HBM2eメモリが 4タイル (スタック) EMIB技術を用いて接続される。恐らく、以前は Base Tile にそれぞれ HBM2eメモリが接続される、ということで 2タイルとして計上していたのだろう。

Andreas, in Jan we didn't account the HBM's as individual tiles. That's the main difference.

— Raja Koduri (@Rajaontheedge) March 24, 2021

16 Xe HPC (internal/external)

8 Rambo (internal)

2 Xe Base (internal)

11 EMIB (internal)

2 Xe Link (external)

8 HBM (external) https://t.co/uA0jAs8QDo

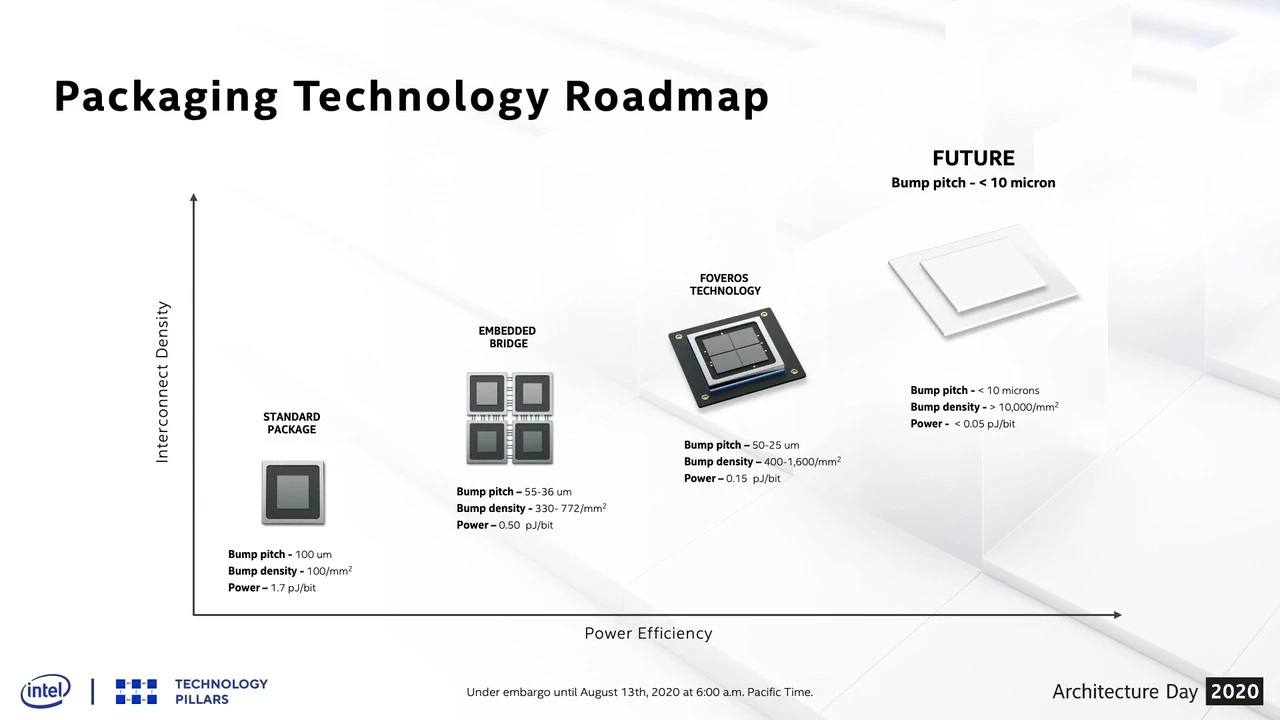

また、氏はIntel社内ではバンプピッチ 55μm以下の高密度実装を必要とするシリコンを「タイル」、標準的なパッケージに実装されるシリコンを「チップレット」と区別していると伝えている。1

バンプピッチ 55μm以下の高密度実装には EMIB (Embedded Multi-die Interconnect Bridge)、Foveros 技術が該当する。

Intel Packaging Technology

画像出典: Video: Architecture Day 2020 (Event Replay) | Intel Newsroom

47個のタイル

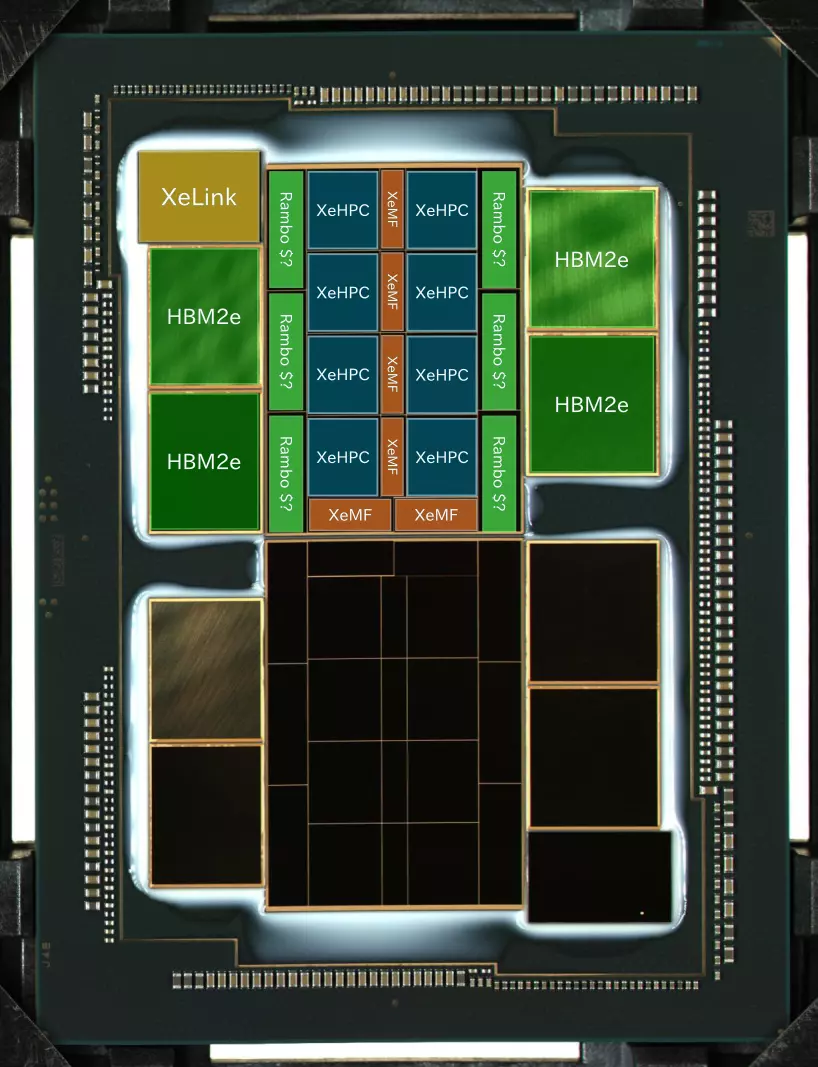

以下は 2021/01/26 に Raja Koduri氏が公開した Ponte Vecchio のパッケージ画像を元に、チップ構成を推測した画像。

Xe-HPC / Ponte Vecchio (v1)

画像元: https://twitter.com/Rajaontheedge/status/1354103878426324994

今回の Raja氏による内訳の説明と合わせれば、まず巨大な長方形をした Xe Base タイルが 2個、 Xe-HPC タイルがそれぞれに 8個、Foveros技術によって積層されている。

また、Xe Base には EMIB技術により HBM2eメモリ 4個と Xe Link タイルが 1個それぞれ接続されている。

それだと 10個の EMIBチップとなるが、2個の Xe Base タイル同士もまた EMIB で接続されるため、それを合わせて 11個となる。Xe Base のような Foveros技術を用いるタイル同士には Co-EMIB という名称が使われる。

Rambo Cache タイルについては以前、Xe Base の端に位置するタイルがそうではないかと推測したが、各 4個ということから、 Xe-HPC の間に位置するタイルが Rambo Cache タイルだと考えられる。過去の資料を見返してみれば、完全なイメージではあるがそのように説明しているものがあった。2

Rambo Cache タイルもまた Foveros技術によって Xe Base タイルに積層される。

そのタイルからは思っていたよりも小さい印象を受けるが、容量は未公開であり、GPU内のキャッシュ (SRAM) とパッケージ内メモリ (HBM2eメモリ) の間を埋めるメモリ帯域であることだけが発表されている。

端に位置するのはパッディング、ダミーダイの可能性が考えられる。ダミーダイと言っても役割が無い訳ではなく、全体を長方形に整え、主に Xe-HPC タイルから発生する熱を逃し、熱密度を緩和することで冷却を容易にするなどの役割がある。

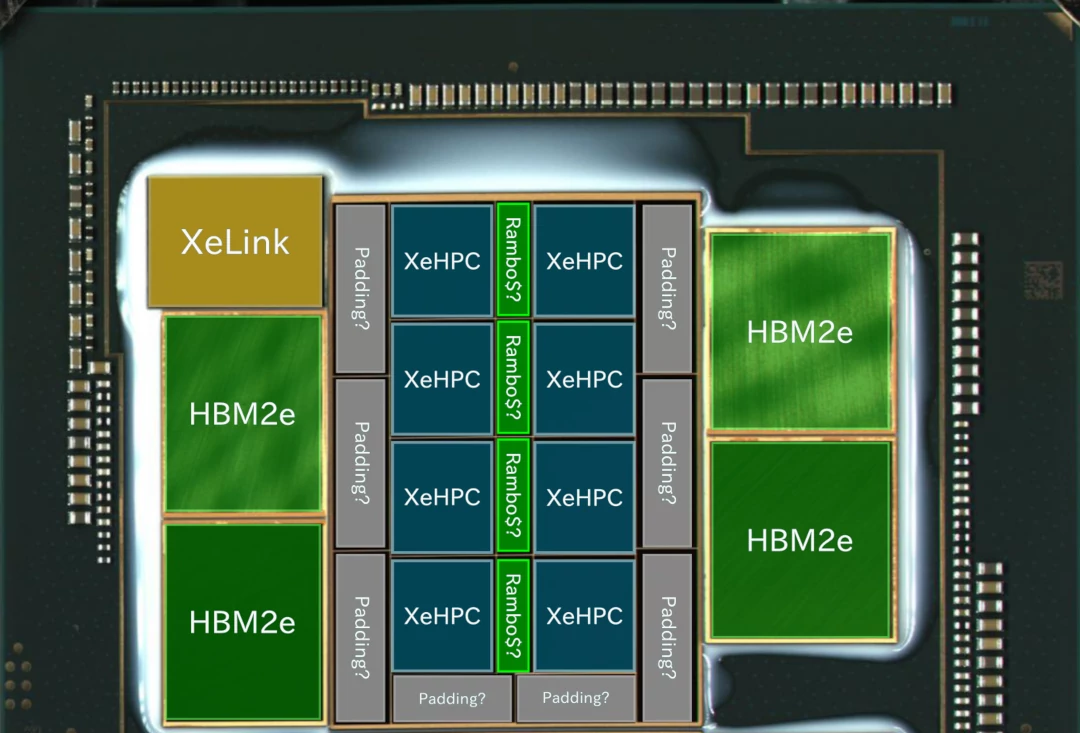

上記を元にアップデートしたのが以下。

Xe-HPC / Ponte Vecchio (v2)

画像元: https://twitter.com/Rajaontheedge/status/1354103878426324994

- Ponte Vecchio

- Base Tile (Intel 10nm SF)

- |+ Foveros +| 8x Xe-HPC/Compute Tile (Intel Next Gen & External)

- |+ Foveros +| 4x Rambo Cache (Intel 10nm eSF)

- | EMIB | 4x HBM2 (External)

- | EMIB | 1x Xe Link I/O Tile (EMIB) (External)

- Base Tile (Intel 10nm SF)

- || Co-EMIB ||

- Base Tile (Intel 10nm SF)

- |+ Foveros +| 8x Xe-HPC/Compute Tile (Intel Next Gen & External)

- |+ Foveros +| 4x Rambo Cache (Intel 10nm eSF)

- | EMIB | 4x HBM2 (External)

- | EMIB | 1x Xe Link I/O Tile (EMIB) (External)

- Base Tile (Intel 10nm SF)

参考リンク

-

Raja KoduriさんはTwitterを使っています 「Internally we also are switching to “tile” nomenclature to differentiate silicon that needs to be packaged with advanced high density packaging (55 micron bump pitches and below) v/s silicon “chiplets” that can be packaged with standard packaging」 / Twitter ↩︎

-

https://s21.q4cdn.com/600692695/files/doc_presentations/2019/11/DEVCON-2019_16x9_v13_FINAL.pdf#page=64 ↩︎