Intel Tremontアーキテクチャを採用するモバイル向けプロセッサ。1

Jasper Lake Spec

| Intel JSL | |

|---|---|

| Memory Interface | LP/DDR4 128-bit? |

| CPU | Tremont (Family: 0x6, Model 0x9C) 2 |

| CPU Core/Thread | (4/4?) |

| L2cache (shared 4-Core) | 1.5MB |

| L3cache/LLC | 4MB |

| GPU | Gen11 |

| Total EU (Sub-Slice x EU) |

16EU(2x8) /20EU(4x5) 24EU(4x6) /32EU(4x8) |

| GPU L3cache | 1280KB (4 Banks) |

| GNA | GNA Gen2 (same TGL-U)3 |

| TDP | 6 ~ ?W 4 |

CPU

CPUアーキテクチャに Tremont を採用することは判明しているが、最大コア数、CPUコア間で共有する L2キャッシュ構成等は不明。

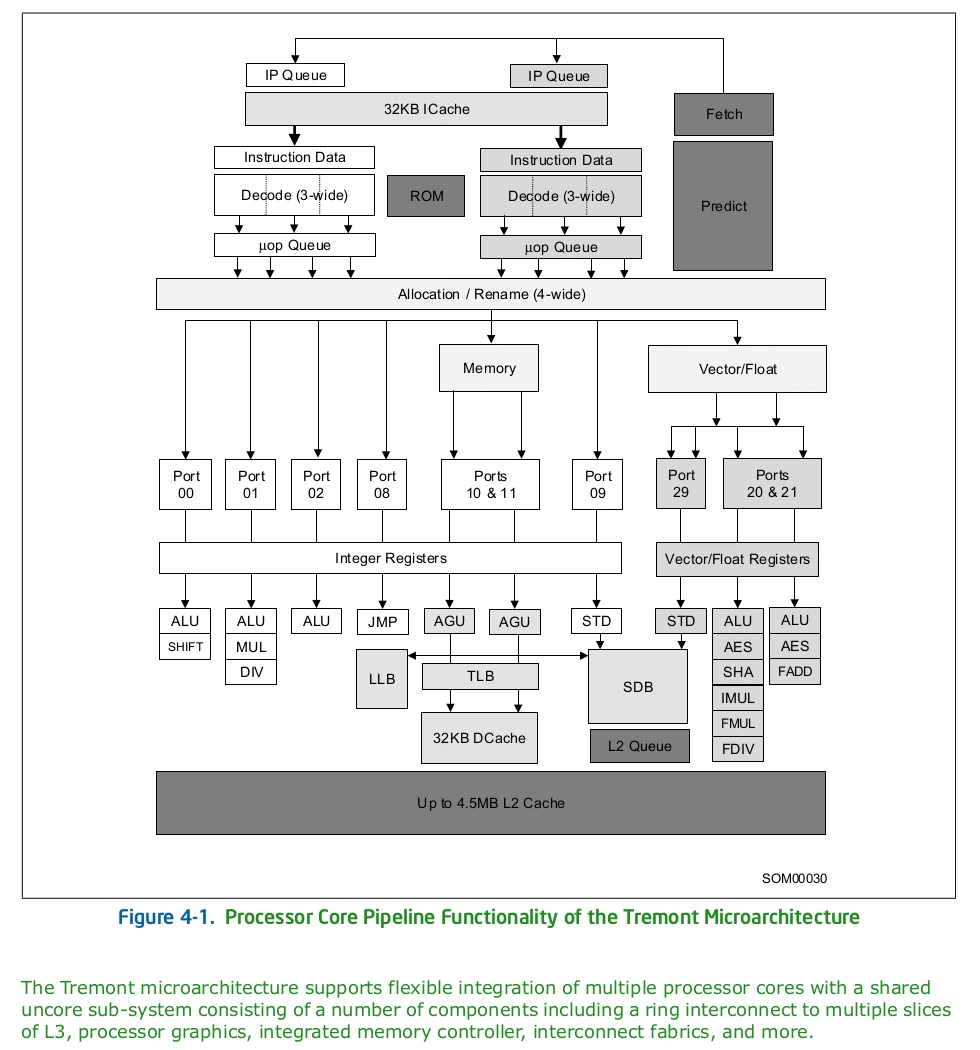

Tremont Architecture

画像出典: Intel® 64 and IA-32 Architectures Optimization Reference Manual

GPU

GPU の仕様は、同様に Tremontアーキテクチャ を採用する Elkhart Lake とほとんど共通している。そのため、GPUドライバーの記述では Elkhart Lake とされている場合もある。

規模やディスプレイ周りの仕様は多少異なるとされる。

GPUアーキテクチャは Gen11。5

Ice Lake と同じだが、intel/media-driverの記述を読む限り、ハードウェアの固定機能部に合わせてシェーダーを用いるエンコードや映像の後処理(フィルター、デノイズ) 機能が Ice Lake とは違いサポートされていない。

だがソフトウェアの将来的なアップデートでサポートされる可能性はある。

GPUのシェーダー部、Slice/Sub-Slice/EU の構成には 5種類が存在する。EU数で言えば、16EU/20EU/24EU/32EU の 4種類となる。

CHIPSET(0x4E51, ehl_4x4, "JSL", "Intel(R) UHD Graphics") CHIPSET(0x4E55, ehl_2x8, "JSL", "Intel(R) UHD Graphics") CHIPSET(0x4E57, ehl_4x5, "JSL", "Intel(R) UHD Graphics") CHIPSET(0x4E61, ehl_4x6, "JSL", "Intel(R) UHD Graphics") CHIPSET(0x4E71, ehl_4x8, "JSL", "Intel(R) UHD Graphics")引用元: include/pci_ids/i965_pci_ids.h · 559b26b7ee093c2cbe446bf8023876642deadcee · Mesa / mesa · GitLab

Slice数は 1基で固定、Sub-Slice数は 2基または 4基、Sub-Slice あたりの EU数は 4/5/6/8基のどれかとなっている。

総 16EUとなる構成には、Sub-Slice数 2基、それぞれの EU数は 8基という構成と、Sub-Slice数 4基、それぞれの EU数は 4基という構成の 2種類がある。

Sub-Slice 内には、テクスチャサンプラーやローカルメモリ等のリソースが含まれるため、性能では後者の Sub-Slice数 4基の構成が高くなるのではないかと考えられる。

Chromebook

Jasper Lake を搭載するChromebookボードは、メインボードがコードネーム Dedede であり、実際に製品に採用される派生ボードにも星のカービィに関連したコードネームが付けられている。

- Dedede (Main Board)

- Boten

- Drawcia

- Madoo

- Waddledoo

- Wheelie

- Magolor

参考リンク

-

x86/cpu: Add Jasper Lake to Intel family · torvalds/linux@b2d32af ↩︎

-

acrn-kernel/gna_pci.c at 30000faef6e05a0e2430ff2a7f61539f86970d70 · projectacrn/acrn-kernel ↩︎

-

https://review.coreboot.org/c/coreboot/+/41668/6/src/mainboard/google/dedede/variants/baseboard/devicetree.cb ↩︎

-

intel: Add device info for 1x4x6 Jasper Lake (11fdd5f5) · Commits · Mesa / mesa · GitLab ↩︎