異なる種類のコアを 1つのSoC/プロセッサに搭載するハイブリッドコア技術を、Intel は Lakefieldで実用化し、続く Alder Lake ではデスクトップ向けにも導入すると目されている。

AMD もまたハイブリッドコア技術に関する特許を提出しており、注目を浴びている。

AMD の省電力に向けたハイブリットコア技術を読む | Coelacanth’s Dream

ハイブリッドコアは主に、高性能、高機能でダイエリアを大きく取るコア(big /High /Core系コア) と、

性能、機能面では big /High /Coreコアより劣るが、電力比性能で優れ、占有するダイエリアが小さいコア(small /Low /Atomコア) の 2種類を用いて構成される。

このハイブリッド技術に関して、ただ私見を書いていく。

先に書くと、以前書いた Alder Lake の推測だいぶ被る内容となっている。1

ダークシリコン問題

ずっと以前より、消費電力、電力密度、発熱等から、ダイ上に同時には電力を供給できない部分が出てくる ダークシリコン問題 が顕在化していた。

この問題に対し、CPUベンダーはプロセッサに CPU とは別に、ある特定の用途に対して効率的に処理ができるユニットを搭載したり、または、シングルコアではあるクロックを設定できるプロセッサに対し、全てのコアに負荷が掛かる場合はクロックをそれよりも制限することで対処してきた。

例えば、Intel はある世代から同じダイに CPU と GPU を搭載し、時には GPU に半分近くのダイエリアを割くことでダークシリコン問題を軽減してきた。それ以外にも Ice Lake (Client) に Thunderbold 3 のコントローラーを搭載するなどしている。

このダークシリコン問題により、仮に big /High /Coreコアを多数搭載したとしても、消費電力、発熱等によって最大クロックは制限され、ピーク性能は下がる。そのことはトランジスタ数効率の悪化も意味する。

トランジスタ数が多ければリーク電流もまた増大するため、トランジスタ数効率の悪化は大きな問題と言える。

性能がトランジスタ数、ダイサイズに見合わないとなると、生産コストが重く伸し掛かるという商業的な問題もあるだろう。

ハイブリッドコア構成の利点

Alder Lake に導入されるハイブリッドコア(Core/Atom)技術もまた、ダークシリコン問題対策の意味を含んでいるのではないかと自分は思う。

small /Low /Atomコアも搭載することでダークシリコン問題を軽減しつつ、GPU を多く搭載するのとは別アプローチで CPU 性能を向上させる。

搭載する GPU の規模を増やすことでは、特定の処理を割り振ったり、ダークシリコン問題を軽減した分 CPU の最大動作クロックを伸ばすぐらいでしか性能を向上させられなかった。

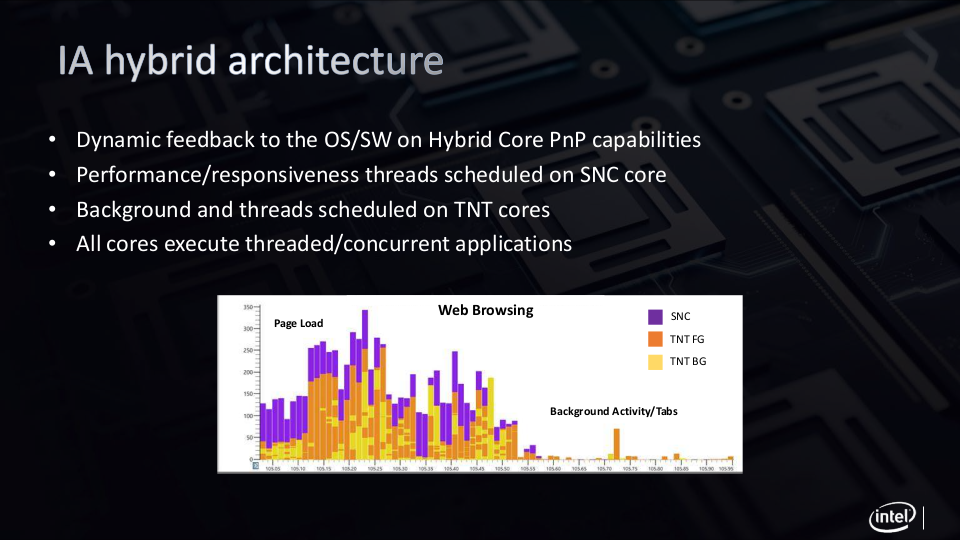

しかし Intel が Lakefield で示したように、small /Low /Atomコアにバックグラウンドタスクや軽い処理を割り振ることで、CPU 全体の性能に直接的に影響させつつ、動作時の消費電力を最適化することができる。

LKF Workload

画像出典: https://www.hotchips.org/hc31/HC31_2.10_LKF_HC_2019_Final_v7.pdf

先日の AMD のハイブリッドコア技術は、電力効率に優れる Lowコアを搭載し、高性能な Highコアと対応させることで幅広い範囲の電力比性能をカバーするものだったが、

Intel が Lakefield に導入したハイブリッドコア技術では、全てのコアが同時に処理に行なえるため、スケジューリング等の壁はあるだろうが

重い処理は Coreコアに、バックグラウンドタスク、軽い処理はAtomコアに割り振ることで電力効率の良い処理が可能だろう。

そういったトランジスタ数効率、電力効率に優れるハイブリッドコア技術に対し、Cinebench のようなシンプルなベンチマークソフトウェアではその真価を測りづらい。

様々な種類の、その時で異なる負荷が掛かるような、現実的な ベンチマークが必要となる。

このことが近年の Intel が示す、人気のベンチマークソフトウェアへの一部否定的な姿勢ではないかと考えている。